알아야 할 것 : Interrupt의 필요성, 과정, 종류

Interrupts

Interrupt Mechnism

Interrupt의 필요성을 알아보자

프로세서의 utilization (사용성)을 향상시켜야한다.

- 대부분의 I/O 디바이스들은 프로세서보다 느리다.

- 프로세서는 디바이스를 기다리기 위해서 (pause) 하던 일을 멈춰야한다. -> busy waiting

- 즉 프로세서의 낭비가 있다 !

- 예를 들어서, write 작업을 하던 도중에 프린터를 쓰면 프린터 작업이 완료될 때까지 write를 중지하고 idle(쉬는상태) 상태를 유지해야한다.

고로 프린터를 사용하던 도중에는 idle 상태가 되니까 이 상태를 프로세서의 낭비가 있다고 한다.

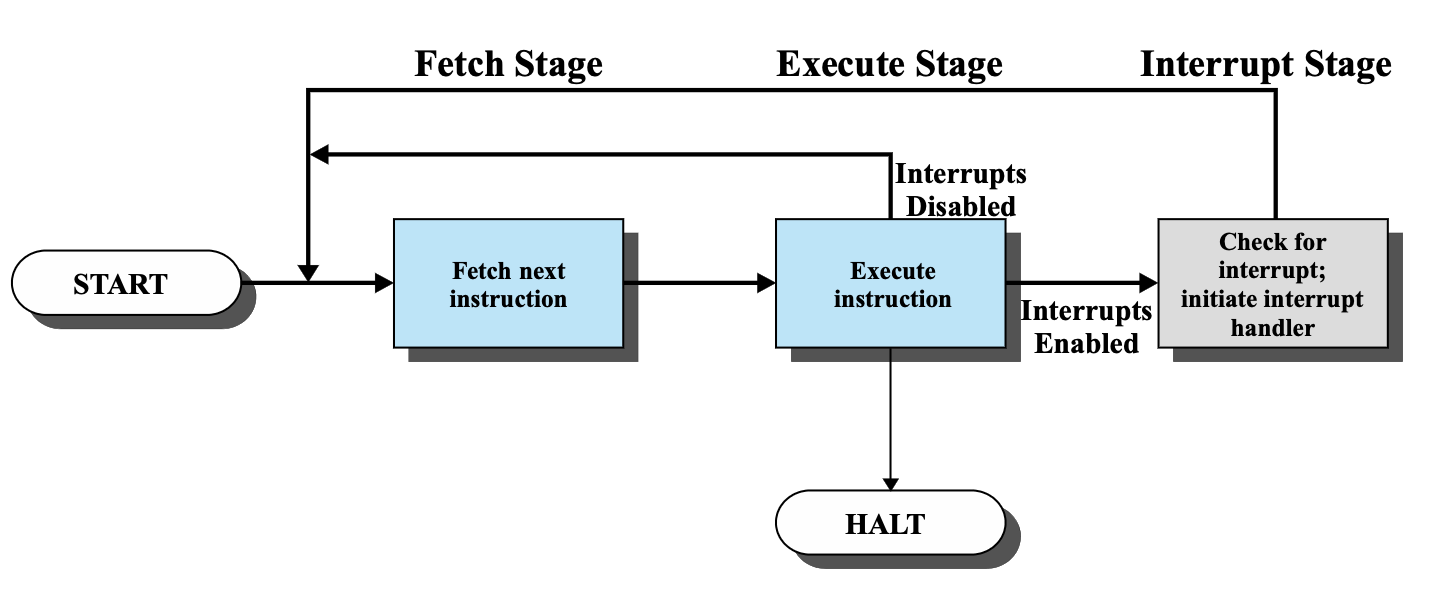

Interrupt를 포함한 Instruction Cycle (명령어 사이클)을 알아보자.

- 시작 !

- 다음 instruction을 Fetch

- instruction을 실행시킨다. (세가지 상황 발생)

- Interrupts Disabled: 인터럽트가 발생하지 않았으면 다음 명령어를 계속 실행한다.

- Interrupts Enabled: 인터럽트가 발생했으면 interrupt handler를 정의해서 인터럽트를 실행한다. 실행 후 원래의 명령어를 실행후에 원래의 프로세스로 돌아간다.

- HALT (정지)

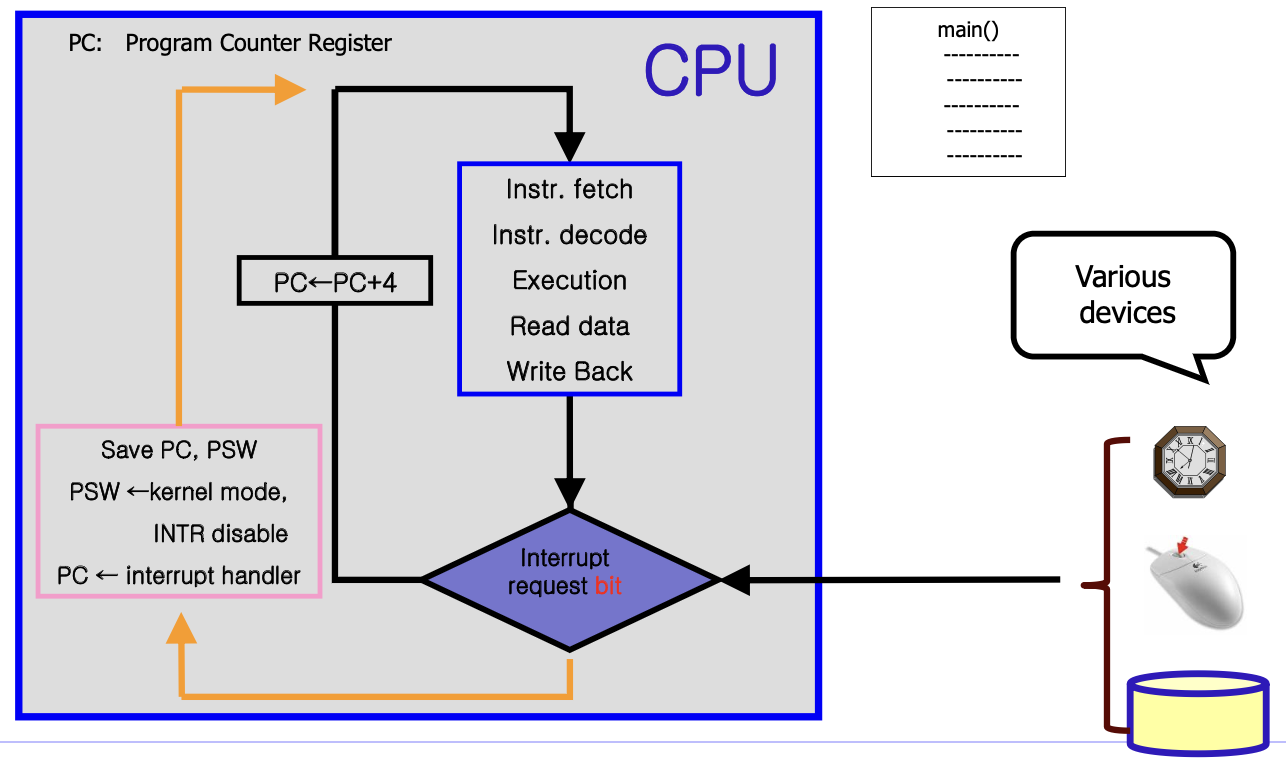

더 자세히 Interrupt 의 과정을 알아보자

CPU 에서 PC를 증가시켜가면서 명령어를 수행하고 있었는데, (Interrupt request bit 가 0 일때)

다른 디바이스들에서 PIC로 신호를 보내 Interrupt request bit가 1이되어 인터럽트가 발생하였다.

이 때 재빨리 해야할 일은 PC와 PSW를 저장하는 것이다. (주황색 선)

PSW 란, 특별한 목적의 레지스터로 Program Status Word의 약자이다.

- PSW 에서 privilege mode 를 kernel mode 로, INTR disable 로 해야한다.

- (Interrupt 는 kernel 함수의 일종이므로, kernel mode에서만 동작하기 때문에 user mode 에서 kernel mode로 바꿔주고, 잠시 다른 Interrupt를 받지 않게 INTR disable을 설정한다.)

- PC에는 실행할 Intterupt handler 의 주소를 넣어야 한다.

만약 save 주소를 저장하지 않으면 원래 프로세스로 돌아갈 수가 없다. ㅠ

PC와 PSW에 저장했으면, kernel mode로 들어와서 PC, PSW를 제외한 모든 레지스터를 저장한다. (save all, 공통과정)

각각 타이머, 디스크, 마우스같은 디바이스의 리퀘스트 벡터를 실행하는 함수인 Interrupt Service Routine 을 실행한다.

ISR = Interrupt Service Routine

번외

Interrupt handler 와 ISR 을 비교하면

| Interrupt handler | ISR (Interrupt Service Routine) |

| 인터럽트가 발생했을 때 실행하는 공통과정 (전과정) | 디바이스들의 특수과정을 실행하는 함수 |

하지만 구분하지 않고 사용할 때도 있다고 한다~

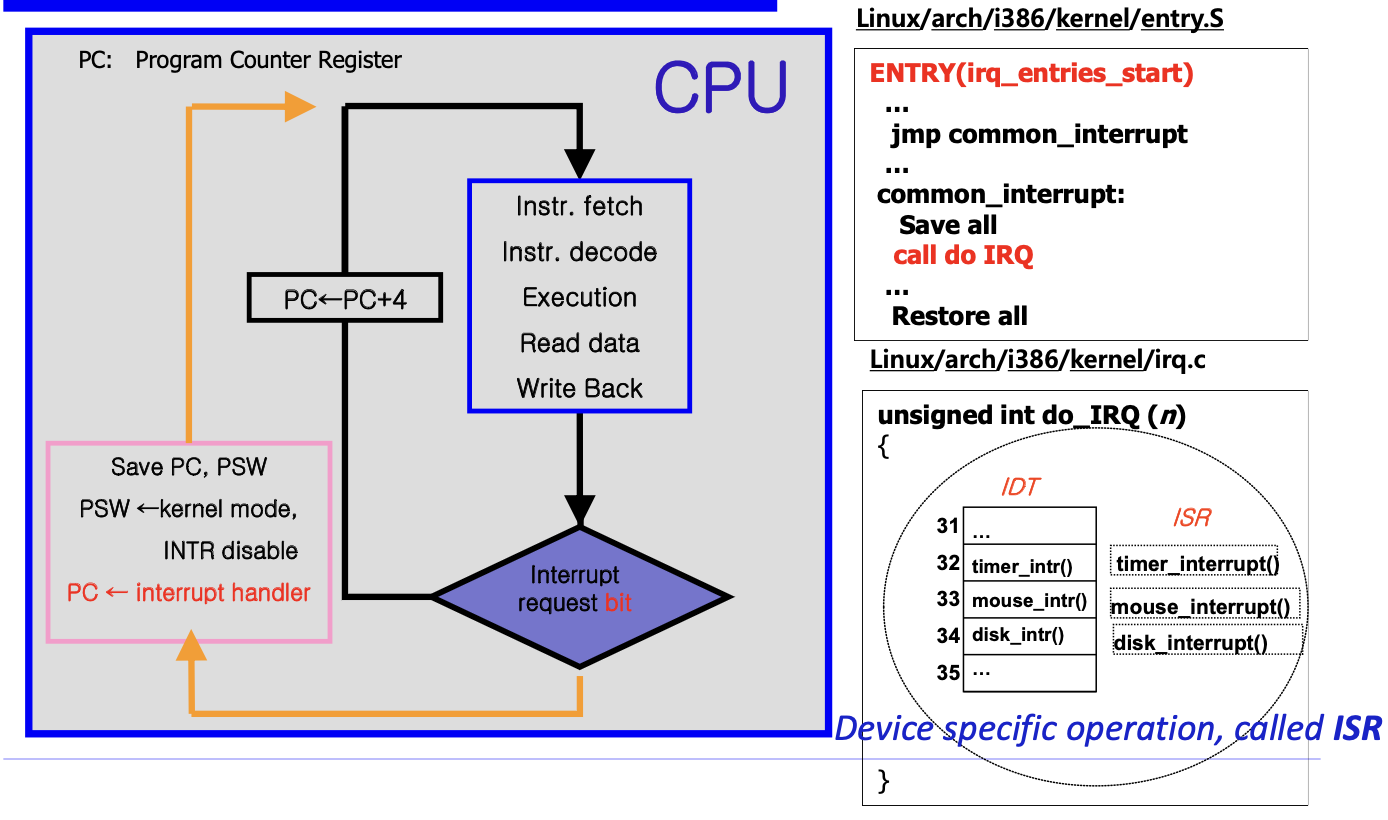

리눅스에서의 예시

ENTRY : 커널로의 진입점

do IRQ : 리눅스에서 Interrutp 를 handling 하는 코드 (c언어)

오른쪽아래의 do_IRQ를 살펴보자

IDT는 Interrupt Decriptor Table 로 각 인터럽트를 실행할 함수의 주소 (ISR) 를 가지고 있는 테이블이다.

(IVT 라고 Interrupt Vector Table 이라고도 한다.)

오른쪽의 두 칸을 위아래로 나눠서 위에는 common operation- 공통과정, 아래는 specific operation- 특수과정 이라한다.

이제 이 전체 과정을 한번에 다시 정리해보자.

Interrupt Processing

- 디바이스 컨트롤러나 다른 시스템 하드웨어에서 인터럽트를 발생시킨다 (PIC).

- 프로세서가 현재의 명령어를 끝낸다.

- (프로세서가 ACK을 보낸다.)

- 프로세서가 PC와 PSW를 저장한다.

- 프로세서가 인터럽트 핸들러의 주소를 PC에서 가져와 로드한다.

- Save all - PC와 PSW를 제외한 남은 모든 정보를 저장한다.

- ISR - 인터럽트를 실행한다.

- Restore all - 프로세스의 모든 상태 정보를 가져온다.

- Restore old PSW and PC - 프로세스의 PC와 PSW를 가져온다.

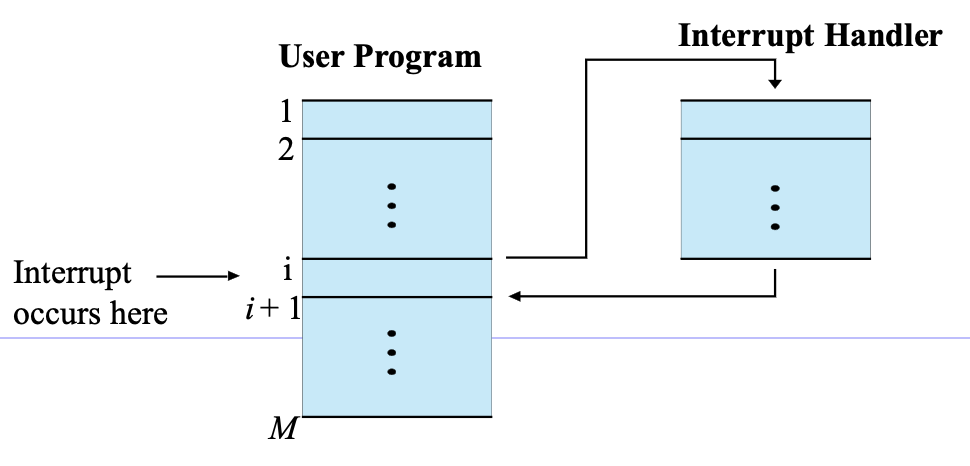

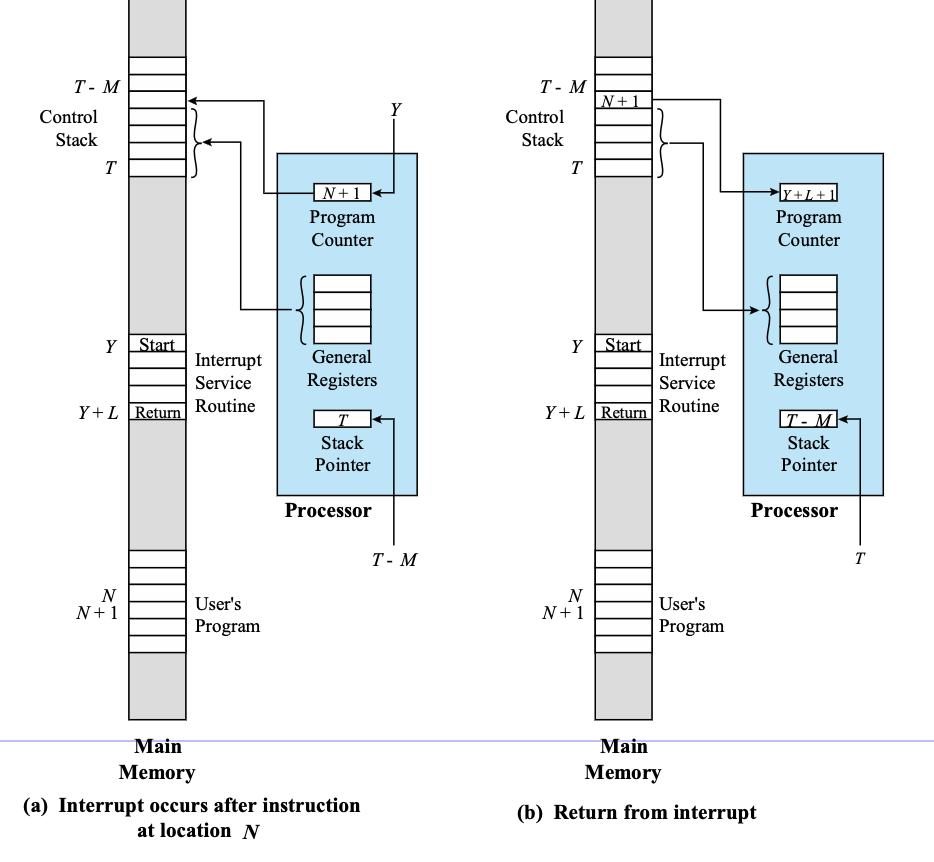

이 과정을 다시 메모리를 통해서 보자 아 힘들다

(a) 왼쪽 그림은 User's Program 을 실행하는 도중에 N 의 명령어 이후에 인터럽트가 발생한 그림이다.

파란색 프로세서에서 PC에 다음에 실행할 N+1 을 저장하고, 다른 레지스터의 정보들도 모두 저장한다.

(b) 오른쪽 그림은 인터럽트가 끝나고 난 직후의 (restore 전) 그림이다. 만약 원래 PC 인 N+1를 저장하지 않았다면, ISR의 마지막 Y+L 의 다음인 Y+L+1 이 PC에 들어가 실행됐을 것이다.

위에서 계속 말했던 ISR (Interrupt Service Routine) 에 대해 또 자세히 알아보자 ~

ISR (Interrupt Service Routine) : Device specific operaion 디바이스 특수 명령어 ~

위에서 배운 리눅스 do_IRQ 함수를 자세히 보면 !

우선 인자로 받는 regs 는 레지스터들이고,

irq_desc 가 위에서 IDT 인 Intrrupt descriptor Table 이다.

-------------여기 다시듣고 다시 적기-----------------

Interrupts 와 Exception 을 알아보자

Interrupts 에는 두가지 종류가 있다.

- Asynchronous interrupts (비동기적 인터럽트) 주로 Interrupt

- 하드웨어 디바이스에서 발생한다.

- External interrupt 외부 인터럽트: 주변장치에서 발생한다.

- Synchronous interrupts (동기적 인터럽트) 주로 exception (trap)

- CPU 에서 발생한다.

- Exception: 'divide by zero', 'segmentation faults', 'page faults'

- 소프트웨어 인터럽트 !

리눅스에서는 인터럽트와 익셉션이 같은 방식으로 핸들된다고 한다.

Exception

고로 이 그림은 리눅스에서의 exception 과정

명령어 수행과정 (작은 파란박스) 에서 불법 opcode, 불법 address, divide by zero 등 동기적 인터럽트(익셉션)이 발생하면 인터럽트 리퀘스트 비트를 설정한다.

Interrupt 와 Exception 비교

| Interrupt | Exception |

| CPU 외부에서 발생한다. | CPU 내부에서 발생한다. (현재 명령을 실행하는 도중에 발생한다. |

| clock에 비동기적으로 발생한다. | clock에 동기적으로 발생한다. |

| 현재 instruction 이 끝난 후 | 현재 instruction 이 끝나지 못한다. |

| ex) I/O devices, timer, hardware failure | ex) Program: 비정상적인 조건 - illegal opcode, illegal address, divide by zero |

프로그램의 Flow를 살펴보자

(a) 인터럽트가 없을 경우: 1 - 4 - (대기) - 5 - 2 - 4 - (대기) - 5 - 3

(b) 인터럽트가 발생, 짧은 I/O: 1 - 4 - 2a - 5 - 2b - 4 - 3a - 5 - 3b

(c) 인터럽트가 발생, 긴 I/O: 1 - 4 - 2 - (대기) - 5 - 4 - 3 - (대기) - 5

Program Timing: Short I/O Wait

Program Timing: Long I/O Wait

Multiple Interrupts

여러개의 인터럽트를 처리하는 방법은 두가지가 있다.

- Sequential Interrupt processing 순차적 처리

- 정의: interrupt가 실행중일 때 interrupt를 비활성화 시킨다.

- 프로세서가 새로운 interrput 요청 시그널을 무시한다.

- 일반적으로 보류 상태로 남아 있으며 프로세서가 interrupt를 다시 활성화 한 후에 프로세서에서 확인한다.

- 장점: 단순한 구조

- 단점: 상대적 우선 순위 또는 시간이 중요한 요구 사항을 고려하지 않는다.

- 정의: interrupt가 실행중일 때 interrupt를 비활성화 시킨다.

- Nested interrupt processing

- 정의: Interrupt가 발생이 되고 그에 대응되는 Interrupt Service Routine(ISR)을 실행중에 해당 Interrupt나 혹은 다른 Interrupt가 발생되는 경우 먼저 발생된 ISR을 다 마치지 않고 새로 발생된 ISR을 처리하는 것

- interrupt의 우선순위를 정한다.

- 낮은 우선순위의 interrupt를 수행하는 동안 더 높은 우선순위의 interrupt를 수행할 수 있다.

- 높은 우선순위의 ISR이 interrupt되면, 현재 상태는 control stack에 push 된다.

- 장점: 복잡한 구조 (비용이 더 든다.)

- 단점: 우선순위를 고려하여 처리할 수 있다.

- 정의: Interrupt가 발생이 되고 그에 대응되는 Interrupt Service Routine(ISR)을 실행중에 해당 Interrupt나 혹은 다른 Interrupt가 발생되는 경우 먼저 발생된 ISR을 다 마치지 않고 새로 발생된 ISR을 처리하는 것

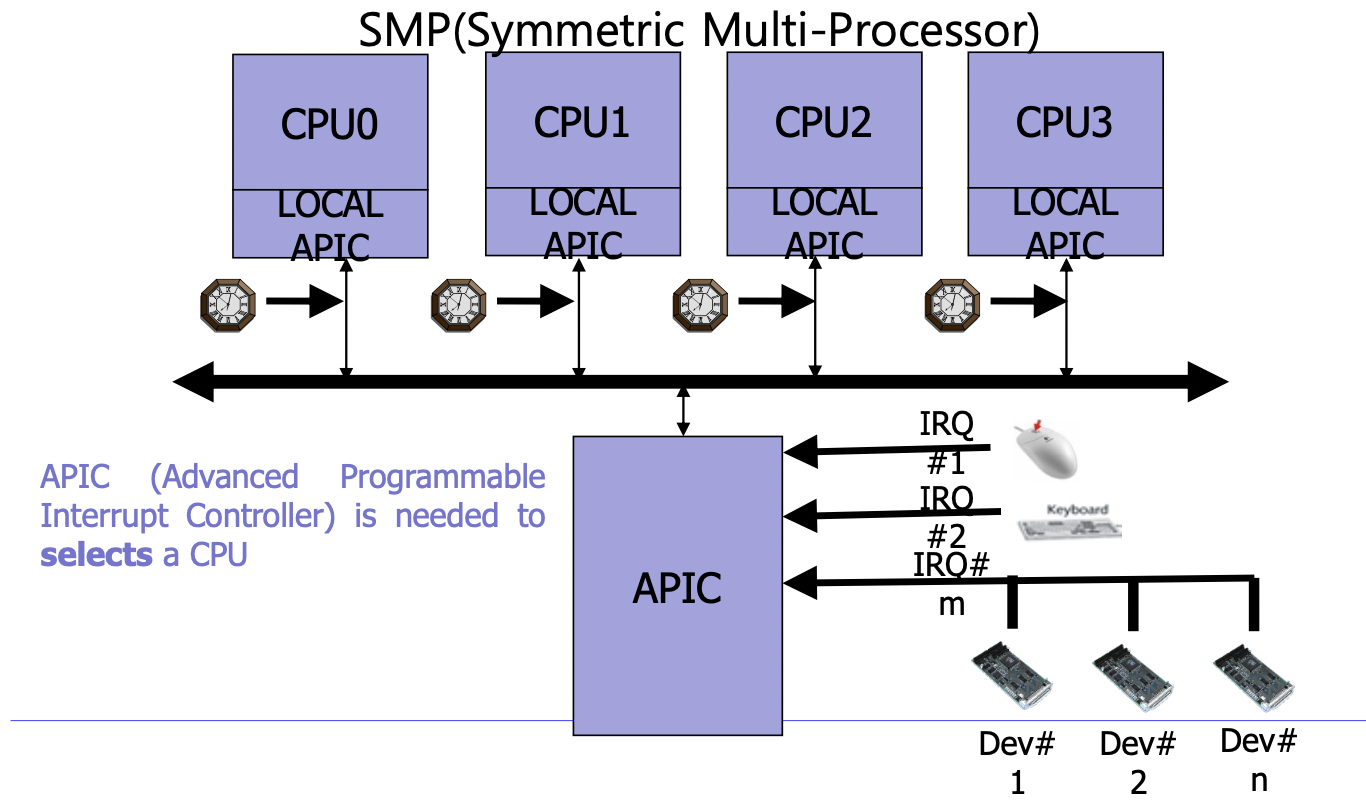

Advanced PIC (APIC) for SMP

SMP (Symmetric Multi-Processor): 다수의 CPU가 동등한 레벨에서 동등한 일을 처리하는 모델

APIC

- 일을 시킬 CPU를 선택해야한다.

- 대부분의 현대 시스템에서 사용된다.

- 적절한 LOCAL APIC으로 신호를 전달한다.

- I/O 디바이스들이 공유한다! (IRQ#1, #2...) IRQ = Intrrupt Request

LOCAL APIC (LAPIC)

- SMP에서 각 CPU마다 하나씩 존재한다.

- 예시로 Timer interrupt를 담당한다.

- 모든 LAPIC는 external APIC(위의 APIC)와 연결되어 있다.

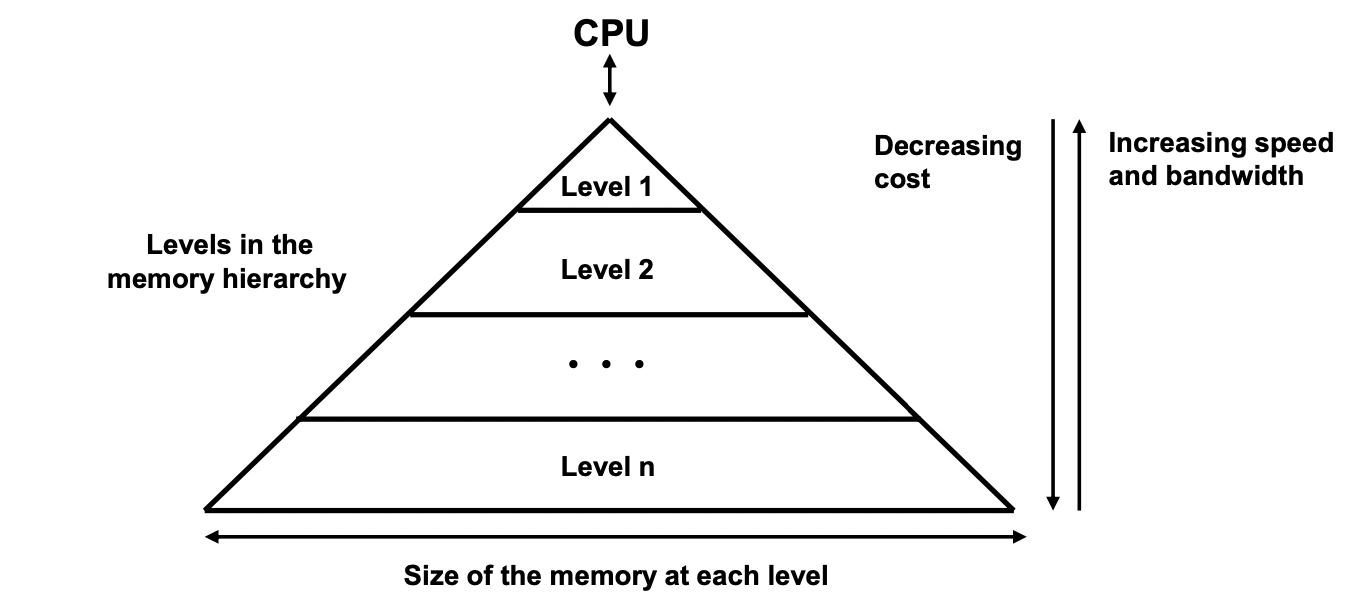

Memory Hierarchy

Memory의 요구사항 세가지 !

- Speed

- Cost

- Size

CPU는 빨라서 기다리게 하면 안된다.

이 세가지를 만족시켜야하는데, 쉽지않다.

그래서 사용자에게는 빠르고 사이즈가 큰 memory가 있는 것처럼 제공한다. (virtual memory)

= Cost가 낮은 메모리로 Speed가 빠른 것을 제공

메모리 계층 구조와 두 가지 유형의 program locality 간의 완벽한 일치로 인한 최적화

이게 무슨소리일까..

우선 locality의 정의를 보면

locality: 기억 장치 내의 정보를 균일하게 접근하는 것이 아닌 어느 한순간에 특정 부분을 집중적으로 참조하는 특성

그러니까 locality라는 특성은 메모리 어떤 부분에 접근할 때 최근에 접근한 영역이나 가장 접근하기 가까운 영역에 접근한다는 것이다.

대표적인 종류 2가지를 보자.

- Temporal locality (locality in time)

- 참조되면 곧 다시 참조되는 경향이 있다.

- 한번 접근이 이루어진 주소의 메모리 영역은 자주 접하게 된다는 특성

- ex) stack

- Spatial locality (locality in space)

- 참도되면 주소가 가까운 항목이 참조되는 경향이 있다.

- 접근하는 메모리 영역은 이미 접근이 이루어진 영역의 근처일 확률이 높다는 특성

- ex) array

Memory Hierarchy의 목표는 위에서 말했듯이

가장 낮은 수준의 메모리의 크기와 비용으로 가장 높은 수준의 메모리에 액세스 할 수있는 "가상"메모리 기술을 (환상) 제공하는 것이다.

Memory Hierarchy Terminology (메모리 계층 용어)

Hit

upper level 상위 레벨에서 접근한 데이터가 발견됨

Hit Rate = 상위 레벨에서 찾은 접근 비율

Hit Time = 상위 레벨에 액세스하는 데 걸리는 시간

Miss

하위 수준에서만 액세스 된 데이터가 발견됨

프로세서는 다음 level에서 데이터를 가져올 때까지 기다리고, 그런 다음 액세스를 다시 시작

Miss rate = 1 – (hit rate)

예시)

Level 1의 액세스 시간: 0.1μs

Level 2의 액세스 시간: 1μs

메모리 액세스의 95 %가 레벨 1 (H = 0.95)에서 발견된다고 가정

바이트 액세스에 걸리는 평균 시간 T = (0.95) (0.1us) + (0.05) (0.1us + 1us) = 0.095 + 0.055 = 0.15us

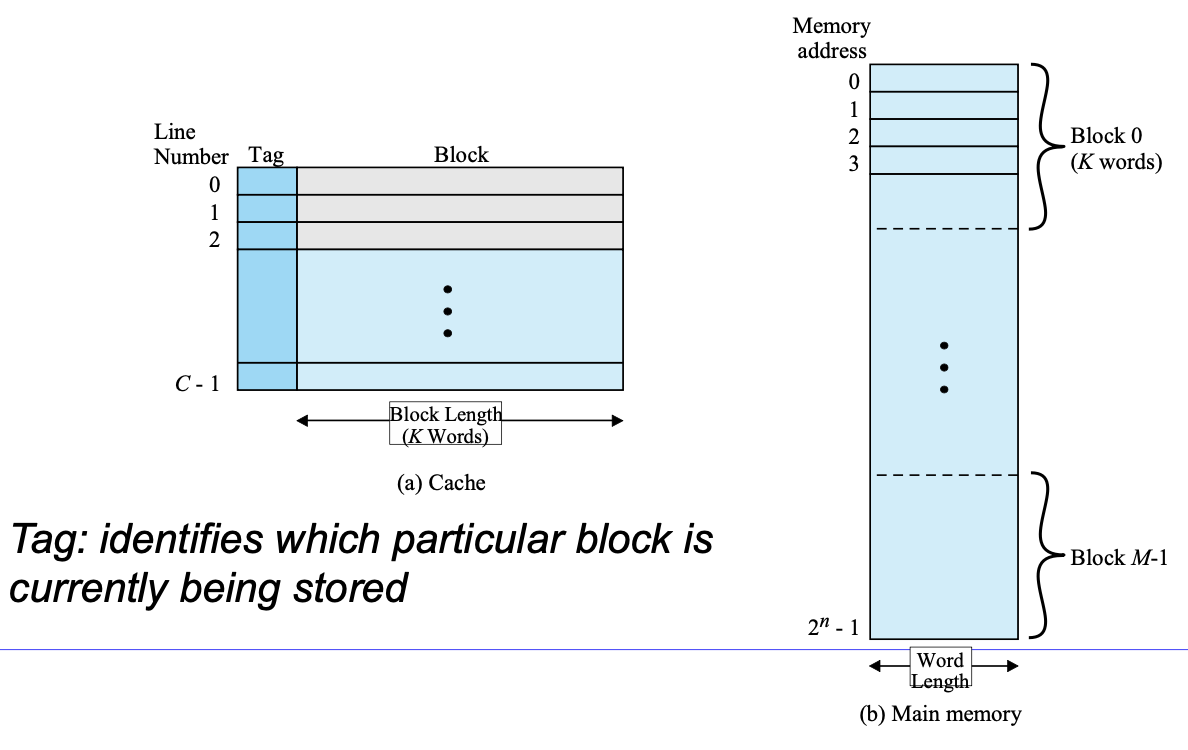

Cache Memory

SRAM 접근시간에 DRAM 사이즈의 메모리에 접근하도록 보이게하는 virtual memory를 제공하는 것이 목표

- Upper level : SRAM (small, fast, expensive)

- lower level : DRAM (large, slow, cheap)

Additional benefits (캐시를 사용할 때 얻는 혜택 !)

- 프로세서가 사용하는 메모리 (bandwidth) 대역폭 감소

- -> I/O를위한 더 많은 메모리 대역폭

- ISA를 변경할 필요 없음 (ISA: Instruction set architecture)

메인 메모리: M = 2^n/K blocks

캐시 : C slots (called line) (C<<M)

C << M: M의 크기가 훨~씬 크다.

캐시는 Tag로 블록 식별이 가능하다.

Cache Organization

Directed Mapped (1-way Set)

2-way Set-Associative

I/O Communication Techniques

'CS > OS' 카테고리의 다른 글

| Thread (2) | 2021.05.17 |

|---|---|

| Process Scheduling 2 (미완) (5) | 2021.05.10 |

| Process Scheduling 1 (2) | 2021.05.09 |

| Operating System Overview (4) | 2021.04.12 |

| Computer System Overview 1 (4) | 2021.03.11 |